## **Avalanche spin-valve transistor**

Cite as: Appl. Phys. Lett. **85**, 4502 (2004); https://doi.org/10.1063/1.1818339 Submitted: 11 June 2004 . Accepted: 10 September 2004 . Published Online: 08 November 2004

K. J. Russell, Ian Appelbaum, Wei Yi, D. J. Monsma, F. Capasso, C. M. Marcus, V. Narayanamurti, M. P. Hanson. and A. C. Gossard

view Online

## ARTICLES YOU MAY BE INTERESTED IN

A spin metal-oxide-semiconductor field-effect transistor using half-metallic-ferromagnet contacts for the source and drain

Applied Physics Letters 84, 2307 (2004); https://doi.org/10.1063/1.1689403

Impedance behavior of spin-valve transistor

Journal of Applied Physics 99, 08H710 (2006); https://doi.org/10.1063/1.2177125

Lock-in Amplifiers up to 600 MHz

## Avalanche spin-valve transistor

K. J. Russell, al Ian Appelbaum, bl Wei Yi, D. J. Monsma, F. Capasso, C. M. Marcus, and V. Narayanamurti

Gordon McKay Laboratory, Harvard University, Cambridge, Massachusetts 02138

M. P. Hanson and A. C. Gossard

Materials Department, University of California, Santa Barbara, California 93106

(Received 11 June 2004; accepted 10 September 2004)

A spin-valve transistor with a GaAs/AlGaAs avalanche-multiplying collector is demonstrated with >1000% magnetocurrent variation and  $\approx 35\times$  amplification of the collector current. The intrinsic amplification of the magnetic-field sensitive collector current should allow fabrication of spin-valve transistors with high gain in a variety of materials. © 2004 American Institute of Physics. [DOI: 10.1063/1.1818339]

With the discovery of the giant magnetoresistance effect<sup>1-3</sup> in magnetic multilayer films, a new class of solid-state magnetic field sensors was developed based on spin-dependent scattering. Among these is the spin-valve transistor,<sup>4-6</sup> which utilizes perpendicular ballistic transport in a metal-base transistor configuration.

In a spin-valve transistor, two magnetic films of different coercivities are spaced by a nonmagnetic layer such that the magnetization of each film can be independently switched by an external magnetic field. As the electrons traverse first one film and then another, spin-dependent inelastic scattering in the magnetic layers selectively thermalizes carriers with spin antiparallel to the magnetization of the layer. Since this is a hot-electron device, carriers that scatter into states with energy below the collector barrier cannot contribute to the collector current. Therefore, if the magnetizations of the films are antiparallel, then the spin species transmitted by the first layer will be selectively scattered by the second, and the collector current will be much lower than the case when the magnetizations are parallel. The percent change in collector current from antiparallel magnetizations to parallel is known as the magnetocurrent variation.

Although the spin-valve transistor can exhibit more than 3000% magnetocurrent variation, <sup>7</sup> its usefulness as a device has been limited by its small collector current (typically  $I_c$  $\sim 10-100$  nA) and low gain (typically  $g=I_c/I_e < 10^{-4}$ , where  $I_e$  is the emitter current). (In nonavalanching transistors in common-base configuration, this definition of gain is also known as the transfer ratio, which is maximally 1 in metal-base transistors.<sup>9</sup>) Thus far, the main approach to increasing the collector current has been to decrease inelastic scattering in the base layer by decreasing the thickness of the base layers <sup>10</sup> or by having one of the ferromagnetic metals as the emitter, <sup>10</sup> or simply by increasing the emitter voltage. <sup>7</sup> This letter presents a complementary method of increasing the gain of a spin-valve transistor that utilizes an avalanchemultiplying collector, without significant decrease in the magnetocurrent variation.

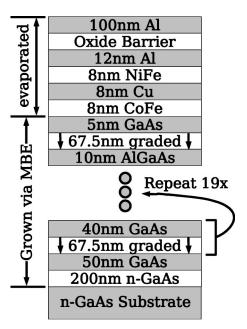

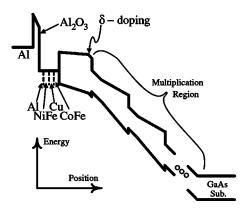

The device presented here (Figs. 1 and 2) is fabricated using shadow mask lithography with previously reported

technology. 11,12 The avalanche-multiplying collector is based on staircase GaAs/AlGaAs avalanche photodiode structures 13,14 that utilize conduction band offsets between GaAs and AlGaAs to enhance the ionization coefficient of electrons. In our structure, the undoped multiplication region consists of alternating spacer layers (40 nm GaAs), where electron impact ionization preferentially takes place, and compositionally graded steps [GaAs (top) to Al<sub>0.45</sub>Ga<sub>0.55</sub>As over 67.5 nm in 1% Al increments with a 1.5 nm period]. The structure is grown via molecular beam epitaxy and comprises (in order from the metal-semiconductor interface to substrate): 5 nm undoped GaAs/graded step/ $1 \times 10^{12}$  cm<sup>-2</sup> *p*-type (Be) δ-doping/10 nm  $Al_{0.45}Ga_{0.55}As/20$  periods alternating spacer and graded step/50 nm undoped GaAs/200 nm n-GaAs doped to  $1 \times 10^{18}$  cm<sup>-3</sup>/n+ GaAs substrate. The  $\delta$ -doped Be layer and graded step near the metal base are included to reduce leakage due to Fowler-Nordheim tunneling of electrons from the base metal into the conduction band of the semiconductor collector at high bias. On top of the collector, the base multilayer is deposited by electron beam

FIG. 1. Schematic diagram of sample structure. See the text for doping information and composition fractions. The arrows in the "graded" regions denote the direction of increasing Al concentration.

a)Electronic mail: krussell@deas.harvard.edu

b)Present address: Electrical and Computer Engineering Department, University of Delaware, Newark, DE 19716.

FIG. 2. Schematic band diagram of the device in operation. The  $\delta$ -doped p-type layer in the collector increases the base-collector barrier, thus reducing the leakage current.

evaporation of the following sequence of metals in a 500  $\times$  500  $\mu m^2$  area: 80 Å  $Co_{0.80}Fe_{0.20}\backslash80$  Å  $Cu\backslash80$  Å  $Ni_{0.84}Fe_{0.16}\backslash120$  Å Al. Next, a thick  $Al_2O_3$  layer (1000 Å) is electron beam evaporated to form an insulating bonding pad. Finally, the exposed Al layer of the base is partially oxidized with an UV- $O_3$  treatment to form the tunnel barrier and two  $\approx$  200  $\times$  100  $\mu m^2$  emitters of 400 Å Al are thermally evaporated to form two side-by-side tunnel junctions. Electrical contact to the base is then achieved by shorting one of the tunnel junctions, leaving the other junction as the emitter. All measurements were performed at 80 K with an emitter-base voltage of -1.5 V, yielding an emitter current of  $\approx$  -4.6 mA.

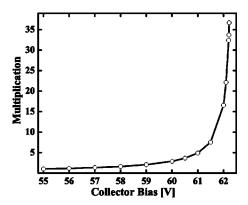

To probe the avalanche multiplication properties of the device, we measured the collector current switching ( $\Delta I_c$  $=I_p-I_a$ , where  $I_p$  is the collector current with magnetic film magnetizations parallel, and  $I_a$  is with magnetizations antiparallel) under various collector biases. The multiplication factor was computed by dividing the value of  $\Delta I_c$  at each voltage by its value at 55 V (a bias below avalanche threshold). This reference voltage is only an estimate due to uncertainty in location of the avalanche multiplication threshold. Since  $\Delta I_c$  is entirely due to ballistically injected electrons, the change in  $\Delta I_c$  with collector bias gives a good measure of the signal amplification. The results, plotted in Fig. 3, show a slow increase in  $\Delta I_c$  as the bias is increased from 55 to 60 V. This slow increase is unrelated to avalanche multiplication, and is primarily associated with the bias dependence of the reflection coefficient of ballistic electrons at the basecollector interface.  $^9$  At  $\approx 60$  V, we see the onset of avalanche

FIG. 3. Multiplication vs voltage of the device at 77 K. Avalanche multiplication can be observed for collector voltages greater than  $\approx 60$  V.

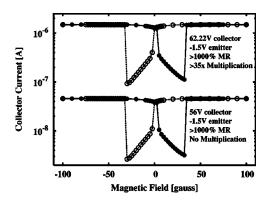

FIG. 4. Magnetoresistance traces at 77 K for collector voltages below (56 V) and above (62.22 V) the avalanche muliplication threshold. Closed circles correspond to a magnetic field sweep from -200 to 200 G; open circles correspond to a sweep in the opposite direction. Avalanche multiplication increases the magnitude of the signal by a factor of  $\approx 35$ , without a significant decrease in the magnetocurrent.

multiplication, and further increases in collector voltage give a rapid increase in  $\Delta I_c$ .

Two representative magnetocurrent traces are shown in Fig. 4, one below avalanche threshold (56 V) and one above (62.22 V). Before each trace, the magnetic field was first swept to -200 G to align the magnetizations of the films, so that each trace entailed a field sweep from -200 to 200 G (closed circles in Fig. 4) and back to -200 G (open circles in Fig. 4) while measuring the collector current. Below avalanche threshold the device exhibits >1000% magnetocurrent variation and  $\Delta I_c \approx 43$  nA. At a collector bias of 62.22 V, the device is in the avalanche multiplication regime, as evidenced by  $\Delta I_c \approx 1.4 \mu A$ . In addition, the magnetocurrent variation at 62.22 V collector bias is still >1000%, indicating that the signal is amplified without a significant contribution from leakage. The gain of the transistor in the two cases is  $g \approx 10^{-5}$  and  $g \approx 3.3 \times 10^{-4}$ , respectively, confirming that the increase in gain is approximately equal to the collector amplification. The slight asymmetry observed at both collector biases is attributed to magnetic film anisotropy.

In an analysis of the signal-to-noise ratio of a device, the utility of avalanche multiplication depends critically on the noise of the amplifier/receiver monitoring the collector current. Avalanche multiplication enhances the total signal-to-noise ratio of the system only in the regime of receiver-dominated noise. Two factors determine the multiplication value that maximizes the signal-to-noise ratio: shot noise of the receiver, and the excess noise factor F associated with avalanche multiplication. For electron-initiated multiplication into an avalanche region with uniform probability of ionization (not a staircase or superlattice structure), F is given by  $^{16}$

$$F = kM + \left(2 - \frac{1}{M}\right)(1 - k),$$

(1)

where M is the multiplication factor and  $k = \alpha_p/\alpha_n$  is the ratio of ionization coefficients for holes and electrons. Most III–V materials have  $k \sim 1$  (e.g., bulk GaAs has  $k \approx 1/2$ ),  $^{17,18}$  which results in a large excess noise factor for any appreciable multiplication. Silicon has  $k \approx 1/30$ ,  $^{16}$  greatly reducing F, and making it a popular material for avalanche multiplication. In the case of GaAs/AlGaAs, superlattice or staircase structures can be used to achieve an effective ratio  $k \approx 1/10$ ,  $^{13}$  and it

has been shown that these structures can exhibit lower excess noise factors than that given by Eq. (1) because the ionization events are localized to the regions of low-band-gap semiconductor adjacent to a potential step. <sup>13,19</sup> Thus, depending on the noise of the receiver, proper device design can result in an avalanche-multiplying collector that enhances the signal-to-noise ratio of the total system.

Other materials such as Si with its small *k* value, or other designs in III–V materials, could possibly yield significant improvements in amplification at lower collector voltages. Ultimately, the choice of material and design for the collector structure will depend on the constraints of the system in which it will be implemented.

In conclusion, an avalanching spin-valve transistor based on structures developed for III–V avalanche photodiodes has been demonstrated. We observed ~35× amplification without significant decrease in magnetocurrent, and we expect that our collector can be both improved and adapted to other materials systems to realize a device structure practical for magneto-electronic applications, as well as novel, optically-read magnetic memory based on luminescent spin-valve transistors. <sup>11</sup>

The authors acknowledge support from the NSF under Contract No. ECS-0322720 and through the NSF funded Nanoscale Science and Engineering Center (NSEC) at Harvard University.

- <sup>2</sup>M. N. Baibich, J. M. Broto, A. Fert, F. Nguyen Van Dau, F. Petroff, P. Eitenne, G. Creuzet, A. Friederich, and J. Chazelas, Phys. Rev. Lett. **61**, 2472 (1988).

- <sup>3</sup>G. Binasch, P. Grunberg, F. Saurenbach, and W. Zinn, Phys. Rev. B **39**, 4828 (1988).

- <sup>4</sup>D. J. Monsma, J. C. Lodder, Th. J. A. Popma, and B. Dieny, Phys. Rev. Lett. **74**, 5260 (1995).

- <sup>5</sup>D. J. Monsma, R. Vlutters, and J. C. Lodder, Science **281**, 407 (1998).

- <sup>6</sup>K. Mizushima, T. Kinno, T. Yamauchi, and K. Tanak, IEEE Trans. Magn. 33, 3500 (1997).

- <sup>7</sup>S. van Dijken, X. Jiang, and S. S. P. Parkin, Appl. Phys. Lett. **83**, 951 (2003).

- <sup>8</sup>D. J. Monsma, Ph.D. thesis, University of Twente, The Netherlands, 1998 (ISBN: 903651049X).

- <sup>9</sup>M. Heiblum and M. V. Fischetti, in *Physics of Quantum Electron Devices*, edited by F. Capasso (Springer, Berlin, 1990), p. 271.

- <sup>10</sup>S. van Dijken, X. Jiang, and S. S. P. Parkin, Appl. Phys. Lett. **80**, 3364 (2002).

- <sup>11</sup>I. Appelbaum, K. J. Russell, D. J. Monsma, V. Narayanamurti, C. M. Marcus, M. P. Hanson, and A. C. Gossard, Appl. Phys. Lett. 83, 4571 (2003)

- <sup>12</sup>I. Appelbaum, D. J. Monsma, K. J. Russell, V. Narayanamurti, and C. M. Marcus, Appl. Phys. Lett. 83, 3737 (2003).

- <sup>13</sup>F. Capasso, W. T. Tsang, and G. F. Williams, IEEE Trans. Electron Devices 30, 381 (1983).

- <sup>14</sup>G. Ripamonti, F. Capasso, A. L. Hutchinson, D. J. Muehlner, J. F. Walker, and R. J. Malik, Nucl. Instrum. Methods Phys. Res. A 288, 99 (1990).

- <sup>15</sup>S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. (Wiley, New York, 1981), p. 767.

- <sup>16</sup>See Ref. 15, p. 770.

- <sup>17</sup>H. D. Law and C. A. Lee, Solid-State Electron. **21**, 331 (1978).

- <sup>18</sup>H. Ando and H. Kanbe, Solid-State Electron. **24**, 629 (1981).

- <sup>19</sup>O.-H. Kwon, M. M. Hayat, S. Wang, J. C. Campbell, A. Holmes, Jr., Y. Pan, B. E. A. Saleh, and M. C. Teich, IEEE J. Quantum Electron. 39, 1287 (2003).

<sup>&</sup>lt;sup>1</sup>H. Sato, P. A. Schroeder, J. Slaughter, W. P. Pratt, Jr., and W. Abdul-Razzaq, Superlattices Microstruct. **4**, 45 (1988).